Tags:CadenceSigrity,仿真

Cadence Sigrity 2019是一款专业的高速电路设计仿真软件,这款软件可以将PCB设计和分析扩展到封装和电路板之外。软件基于Sigrity专利技术,可以有效地提升各类高级物理设计的效率。新版本的Sigrity 2019还带来了全新的功能,优化了工作效率。

主要特色:

• 可以分析板上任意结构的电磁耦合特性,为器件/去耦电容的放置位置以及过孔的排布提供依据

• 可以提取IC封装电源网络与信号网络的阻抗(Z)参数及散射(S)参数,研究电源的谐振频率以及输入阻抗,或研究信号的插入损耗及反射系数,为精确分析电源和信号的性能提供依据; 为时域SSN仿真提供可靠的宽带网络参数模型

• 分析整板远场和近场的EMI/EMC性能,全三维显示复杂的近场辐射水平,为解决板级的EMI/EMC问题提供依据

• 分析板上任意位置的谐振特性,找出系统在实际工作时电源平面上的谐振及波动特性,为电源的覆铜方式及去耦电容的放置位置提供依据

• 支持叠层以及其他物理设计参数的假定(What-if)分析,快速评估设计参数对系统性能的影响

• 基于专利算法的精确直流求解引擎(PowerDC),可支持从直流(DC)到宽频段的精确模型提取

• 与三维(3D)IC封装设计和板级设计工具无缝集成

仿真实例:

高速信号在传输的过程中由于layout走线的不良会导致反射串扰等信号完整性问题,这节我们仿真DDR信号特征阻抗和串扰参数,加深对layout的理解。

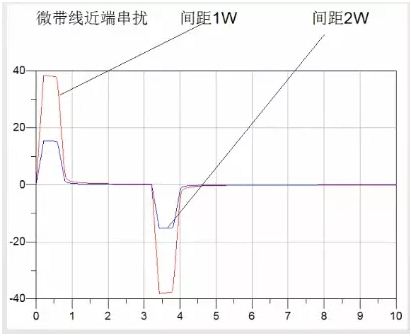

阻抗不匹配导致的反射失真

串扰

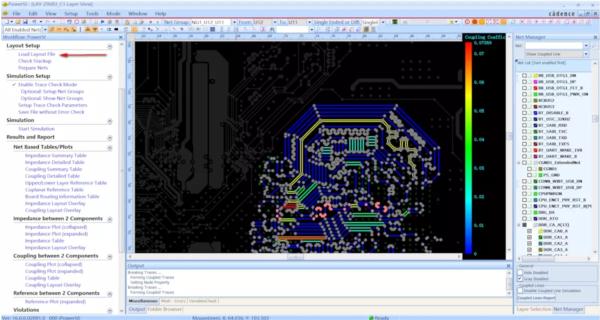

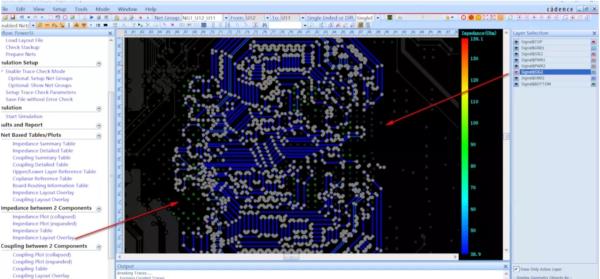

1. 打开PowerSI,load layout file。(我这图是已经仿真完了的)

2. 点击“Setup Net Groups”,选择TX 器件,这里勾选这个线路的CPU U12,点击下一步。

3. 选择RX端,这里勾选这个线路的DDR颗粒U11,点击下一步。

4. 确认电源网络/GND网络,直接点击下一步到分组界面,因为只是练习,我们把DDR的地址和数据等信号都分为一个组,真正项目需要分清楚;点击第一个,再shift点击最后一个,全分为一个组,命名为DDR,然后直接到finish。

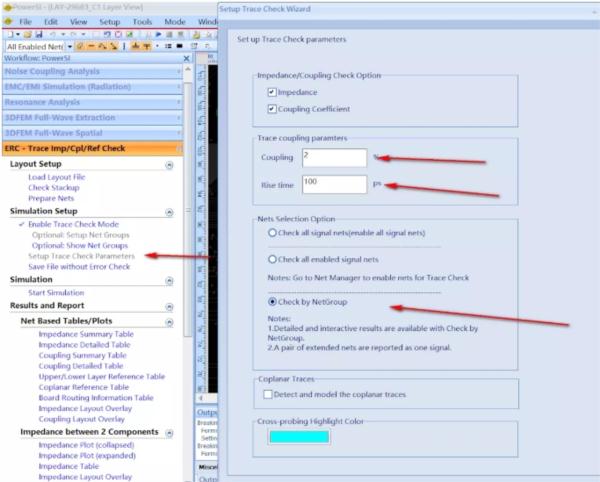

5. 点击“Setup Trace Check Parameters”设置检查参数,默认是勾选阻抗和耦合,设置显示耦合2%以上,选择“根据group检查”,点击OK,开始仿真。

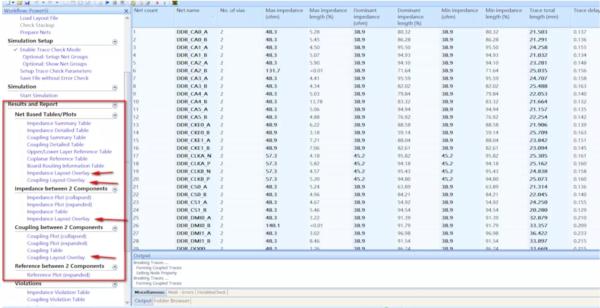

6. 仿真结果又表格形式和layout形式,我们偏向于看layout形式,需要具体点时可以再看表格。

7. impedance layout overlay会将CPU和DDR的走线以layout的形式显示出来,根据颜色区分。

阻抗柱状图也比较直观,每条线摘出来,这里不仅可以看到哪个地方阻抗偏高偏低,还可以看到走线长度。

8. coupling layout overlay通过颜色深浅将串扰强度表现出来,可以看出走线越近的地方串扰越大,一般低于5%信号质量不会受到太大影响。

提取码: 1fu9

中国周易算命网测子女缘(中国周易免费算命网姻缘算命)官方版 | 5.1M

中国周易算命网测子女缘(中国周易免费算命网姻缘算命)官方版 | 5.1M 箫启灵双十一会场推广生成工具免费版 | 1M

箫启灵双十一会场推广生成工具免费版 | 1M 绿叶医疗器械进销存管理系统2017V3官方版 | 46.1M

绿叶医疗器械进销存管理系统2017V3官方版 | 46.1M 闻道倒计时字幕管理V1.2.4 | 1.8M

闻道倒计时字幕管理V1.2.4 | 1.8M 纸币收集管理软件(Liberty Street CurrencyManage 2019)v19.0.0.2免费版 | 170.6M

纸币收集管理软件(Liberty Street CurrencyManage 2019)v19.0.0.2免费版 | 170.6M 腾讯课堂视频批量下载器v3.4 最新免费版 | 19.3M

腾讯课堂视频批量下载器v3.4 最新免费版 | 19.3M 狸窝音轨合并工具(卡拉ok制作工具)【绿色破解版】 | 12.5M

狸窝音轨合并工具(卡拉ok制作工具)【绿色破解版】 | 12.5M 管家通美容美发管理软件v4.0官方版 | 22.4M

管家通美容美发管理软件v4.0官方版 | 22.4M

软件评论 请自觉遵守互联网相关政策法规,评论内容只代表网友观点,与本站立场无关!

网友评论